## 北京锦坤科技有限公司 www.jonkon.com.cn

摘要现代通信系统要求通信距离远、通信容量大、传输质量好。作为其关键技术之一的**调制解调**技术一直是人们研究的一个重要方向。讨论和仿真实现了基于 FPGA 的数字化 <u>DPSK 调制解调</u>系统。用 Altera 公司的 FPGA 开发平台 Quartus II 3.0 实现了一个对基带信号的 <u>DPSK 调制解调</u>系统模型的仿真。

关键词:调制解调 DPSK 现场可编程门阵列(FPGA) Quartus II

中图法分类号 TN919.6; 文献标识码 B

现代通信系统要求通信距离远、通信容量大、传输质量好。作为其关键技术之一的调制解调技术一直是人们研究的一个重要方向。一个系统的通信质量,很大程度上依赖于所采用的调制方式。因此,对调制方式的研究,将直接决定通信系统质量的好坏[1, 2]。随着超大规模集成电路的发展,尤其是微电子技术和计算机技术的迅猛发展和广泛应用,数字化成为目前通信技术发展的趋势,它具有可靠性高、灵活性强、易大规模集成等优点,日益受到重视。目前,数字化的手段主要有专用集成电路(ASIC)和通用数字信号处理器(DSP)。现场可编程门阵列(FPGA)提供了实现数字信号处理的第三种解决方案,它结合了以上两种方式的优势,具有开发周期短、设计方案修改方便、成本低、投资不存在风险问题等[3]。本设计选用了Altera公司的APEX20KE系列的FPGA芯片来实现设计。

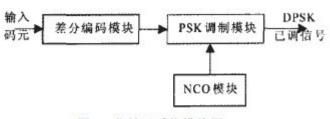

作为 Altera 的新一代开发软件, Quartus II 具有简单易学、易用、可视化、集成化设计环境等优点。Quartus II 支持 VHDL、Verilog HDL 及 AHDL 等多种描述语言。其中 VHDL 和 Verilog HDL 因适合标准化的发展方向而最终成为 IEEE 标准。与 VHDL 相比, Verilog HDL 更容易掌握,并且完成同一功 Verilog HDL 的程序条数一般仅为 VHDL 的 1/3。而且 Verilog HDL 语言可读性强,易于修改和发现错误[4]。本设计采用 Verilog HDL 语言来完成调制解调器的模型设计和仿真。本文是某图像传输扩频系统方案的一部分。研究内容为采用 DPSK 方式完成通信信号的调制解调模型,对扩频和解扩部分不作具体研究,只利用解扩部分产生的位同步信号作为本设计中积分猝灭模块的控制信号。在发射子系统中,首先对基带信号进行差分编码,然后完成 PSK 调制,即 DPSK 调制。PSK 调制实际上是由乘法器完成的,它将差分编码器输出的数据与来自数控振荡器 NCO 的载波相乘,输出的是数字化的已调信号,在整体系统设计中该信号经数模转换后作为中频输出信号[5]。发射子系统模块如图 1。

图1 发射子系统模块图

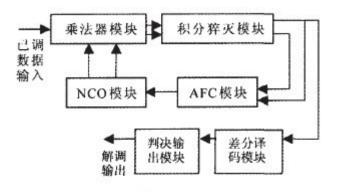

接收子系统是一个相对复杂的数字信号处理系统,它要完成数字中频信号到基带的变换、差分译码和判决输出以及完成自动频率控制。将接收到的经过了模数转换处理的已调数字中频信号分成正交两路,进入乘法器模块与数控振荡器 NCO 输出的两路数字化的正交载波相乘,再经过积分滤波,从而产生基带信号。对此信号进行差分译码,实现对差分编码的逆运算,最后经判决输出恢复出原始信息,实现 DPSK 解调功能。同时,在本系统的设计中,利用在 PSK 解调时产生的包含前后码元相位信息的信号产生自动频率控制(AFC)信号完成对 NCO 模块输出频率的控制和调节,实现 NCO 与中频数字信号的同步控制。系统模块图见图 2。

图2 接收子系统模块图

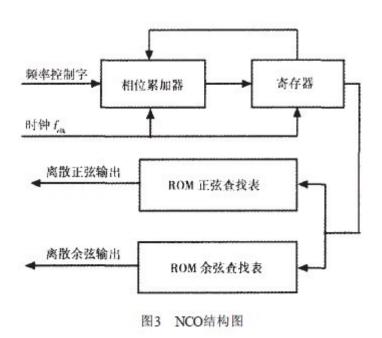

乘法器模块是一个 8 位乘法器,采用的是 ALTERA 的宏功能库中的乘法器,它把经模数变换后输出的 8 位数据分别与 NCO 输出的正交载波相乘。乘积结果为一有符号的 16 位数据。用 Verilog HDL 编程时,则可以以例化的方式调用乘法宏模块。经过乘法器模块出来的数据进入到积分猝灭滤波器,它的作用是进行低通滤波,滤去乘法器模块输出信号中的高频部分。在这里积分猝灭的控制信号即为数据信息码元的位同步信号,它是在伪码同步后产生的,即每经过一个伪码周期产生一个积分猝灭信号,也就是对输入的信号进行累加,每经过一个伪码周期产生一个输出信号: Dot(k)=RΣ(Δτ),输出信号 Dot(k) 和 Cross(k) 作为进行差分译码和鉴相的输入信号。NCO 是基于一个给定频率的信号发生器,其信号的数字化波形可以在一个更高时钟频率下进行相位累加而得到。在这里,需要满足奈奎斯特抽样定理,即待产生的频率低于时钟频率的1/2。数控振荡器一般由相位字寄存器、相位累加器、正弦查找表等部分组成,如图 3。

在系统时钟的作用下,每一个时钟周期存贮在相位字寄存器里的值都由相位累加器进行累加,相位累加器的输出作为正弦、余弦查找表的输入,从而得到相对应的幅度值[6]。系统的频率(f<sub>clk</sub>)决定了输出频率(f<sub>out</sub>,它们的关系如下:

$$f_{\text{cut}} = f_{\text{clk}} M/2^N$$

(1)

N 是相位寄存器的位数, N 值的大小决定了频率分辨率(fres), 有:

$$f_{res} = f_{clk}/2^{N} \tag{2}$$

这样, 当 N 取比较大的数值时, 就具有了很高的频率分辨率[7, 8]。考虑到奈奎斯特抽样定理和其它因素的影响, 实际输出频率一般不应大于  $0.4f_{clk}$ 。在这里 N 取 32,  $f_{out}$  为 10.7 MHz,  $f_{clk}$  为 30 MHz, 所以有:

## $M=2^{32}\times 10.7/30=1531871669$

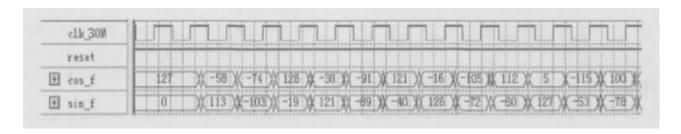

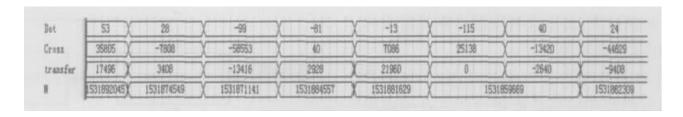

最后得到仿真结果如图 4 所示,输出的结果相当于一个 30 MHz 的采样信号对频率为 10.7 MHz 的 sin ωt 和 cos ωt 信号采样得到的结果。本仿真中,用数字频率合成器产生载波。数字频率合成器的输入时钟为 30 MHz,频率控制字 M 长度为 32 bit,载波频率为 10.7 MHz,根据频率合成器工作原理

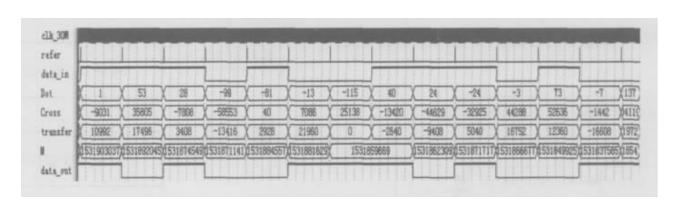

例=2<sup>32</sup> ★ 0.7/30=1 531 871 669。 , 图 5 为解调时载波跟踪的状况, 可见,M 的值在 1 531 871 669 上下波动。"transfer"为由乘法鉴相器的误差信号控制的在频率控制字基础上的波动值,为了保持较好的跟踪特性,在经过截位和乘系数的处理后,其值被控制在正负 30 000 的范围之内。

图 4 NCO 仿真结果

图 5 AFC 模块仿真结果

取图 5 中控制字最小值:Mmin=1 531 859 669 时 NCO 输出频率与中频数字信号的频率差值为:  $\Delta f$ =83 Hz。取控制字最大值:Mmax=1 531 884 557 时 NCO 输出频率与中频数字信号的频率差值为:  $\Delta f$ =90 Hz。 取  $\Delta f$  较大情况的值计算相位误差得: $\Delta \phi$ e =2π $\Delta f$ max /f=0.00072π

可见利用自动频率控制信号可以很好地调节 NCO 的输出频率,使其与中频数字信号达到同步。图 6 是系统的整体仿真图,图 6 左侧为仿真节点。其中"clk\_30M"为 FPGA 工作的主时钟,频率 30MHz。"refer"为主时钟分频得到的数据传送时钟,频率为 256 kHz。也就是说,基带信号传输速率为 256kb/s"data\_in" 为发端待传输数据,码序列"1001110"。"Dot"为 I 路积分器的输出,其值为在一个数据码元时间内以 30 M 时钟采样的 I 路数值的累加,其范围为 24 位的带符号二进制数。"Cross"为 Q 路积分器的输出,也为 24 位的带符号二进制数。"Cross"为 Q 路积分器的输出,也为 24 位的带符号二进制数。"M"为频率控制字。"transfer"为由乘法鉴相器的误差信号控制的在频率控制字基础上的波动值,为了保持较好的跟踪特性,经过截位和乘系数处理后,其值被控制在正负 30 000 的范围之内。"data\_out"为解调后收端得到的数据。由仿真图可知各节点仿真信号时序正确,码元之间相位跳变分明。发端传输的数据经过一定的延时后,与收端得到数据相同,这说明调制数据正确解调,达到系统的要求。进入乘法器模块的信号是经 A/D 转换而来的已调信号。用 8 位的带符号二进制数表示,其范围为-128—127。经过乘法器模块以后,I、Q 分别应该是 16 位带符号二进制数,范围-215—(215—1),这两个信号作为中间变量,没有在仿真图中输出。由于本系统仅是中频以下部分,故实验调试是通过将发射端的输出中频数字信号直接回环到接收端而实现的。因此外部噪声、传输引起的相位漂移、频率漂移影响较小。

致谢:感谢哈尔滨工业大学赵洪林副教授在论文研究期间提供的技术资料和实验设施并进行的耐心指导。

## 参考文献

- 1 昆仑, 郭黎利. 全数字 BPSK 调制解调器. 哈尔滨工程大学学报,2000; (4): 13—19

- 2 Kilfoyle D B, Baggeroer A B. The state of art in underwateracoustic telemetry. IEEE J Oceanic Eng, 2000; 25(1): 4—27

- 3 张佩宗. 利用 FPGA 实现通用解调器. 无线电通信技术, 2001; 27(6): 49—50

- 4 彭保, 吴坚. Verilog HDL 语言在 FPGA/CPLD 开发中的应用. 今日电子, 2004; (5): 34—36

- 5 姜志鹏. 基于 FPGA 的 2DPSK 信号产生器的设计与实现. 现代电子技术, 2003; (21): 28—30

- 6 陈泽强,李蓬勃,曹叶文,毕晓东.基于 FPGA 的数控振荡器设计及其性能分析.山东工业大学学报,2000; 30(6):584—588

- 7 安效军, 王力男. NCO 的数字化实现与应用. 无线电通信技术,2004; 30(2):51—52

- 8 刘玉良, 李远玲. 数字下变频器中数控振荡器的设计与硬件实现.电子技术, 2003; (8): 33—35 图 5 AFC 模块仿真结果 2140

Resear ch on Digital DPSK Modem

SUN Haidan

(Dalian Electronic School, Dalian 116000)

[Abstr act] Long distance, large capability and high quality of transmission are required in modern communication system. Modulation and demodulation, which is one of the most key techniques in communication, has been always an important aspect. The digitalized DPSK modulation and demodulation system

based on FPGA are primarily discussed and simulaed. A model of DPSK modulation and demodulation system

with base band signal are simulated on the basis of a FPGA development platform Quartus II 3.0 developed by

Altera.

[Key words] modulation and demodulation DPSK FPGA Quartus II

北京锦坤科技有限公司 www.jonkon.com.cn